## **SOIC Thin Film on Ceramic Resistor Networks**

### **SOIC-C Series**

# **OBSOLETE**

#### Features:

- Precision ratio tolerances to ±0.05%

- Tracking TCR to ±5ppm/°C

- **Tested for COTS applications**

- Both narrow and wide body versions available

- Standard JEDEC 8, 14, 16 & 20 pin packages

- Ultra-stable TaN resistors on ceramic substrates

- Lower crosstalk than silicon substrate types

All parts are Pb-free and comply with EU Directive 2011/65/EU amended by (EU) 2015/863 (RoHS3)

#### **Electrical Data**

|                                              |        | GS4                               | GS7 | GS8    | GL8  | GL0  |

|----------------------------------------------|--------|-----------------------------------|-----|--------|------|------|

| Package style                                | SOIC-N |                                   |     | SOIC-W |      |      |

| Number of pins                               |        | 8                                 | 14  | 16     | 16   | 20   |

| Element resistance range                     | ohms   | 100R – 200K                       |     |        |      |      |

| Absolute tolerance                           | %      | 0.1, 0.25, 0.5, 1, 2, 5           |     |        |      |      |

| Ratio tolerance to R1                        | %      | 0.05, 0.1, 0.25, 0.5, 1, 2        |     |        |      |      |

| Absolute TCR                                 | ppm/°C | 25, 50, 100                       |     |        |      |      |

| Tracking TCR                                 | ppm/°C | to 5                              |     |        |      |      |

| Element power rating @70°C                   | mW     | Isolated (A): 100, Bussed (B): 50 |     |        |      |      |

| Package power rating @70°C                   | mW     | 400                               | 700 | 800    | 1200 | 1500 |

| Rated operating voltage not to exceed v(PxR) | V      | 100                               |     |        |      |      |

| Operating temperature                        | °C     | -55 to 125                        |     |        |      |      |

| Noise                                        | dB     | <-25                              |     |        |      |      |

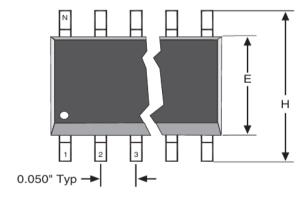

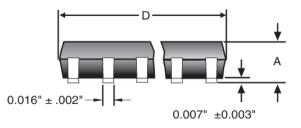

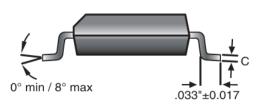

### **Physical Data**

|       |               | D       | Н       | E       | Α       |         |

|-------|---------------|---------|---------|---------|---------|---------|

| Style | Package       | ±0.004" | ±0.008" | ±0.004" | ±0.004" | С       |

|       |               | ±0.1mm  | ±0.2mm  | ±0.1mm  | ±0.1mm  |         |

| GS4   | SOIC-N-8      | 0.193"  |         |         |         |         |

| G34   | 3010-11-8     | 4.9mm   |         |         |         | 0.0075" |

| CS7   | SOIC-N-14     | 0.341"  | 0.236"  | 0.153"  | 0.064"  | ±0.01   |

| G37   | 301C-IN-14    | 8.66mm  | 5.99mm  | 3.89mm  | 1.63mm  | 0.19mm  |

| CCO   | COIC N 1C     | 0.39"   |         |         |         | ±0.25   |

| G38   | GS8 SOIC-N-16 |         |         |         |         |         |

| CLO   | SOIC-W-16     | 0.402"  |         |         |         | 0.011"  |

| GLO   | 301C-W-16     | 10.2mm  | 0.406"  | 0.295"  | 0.1"    | ±0.002  |

| GLO   | SOIC-W-20     | 0.502"  | 10.3mm  | 7.49mm  | 2.54mm  | 0.28mm  |

| GLU   | 301C-W-20     | 12.8mm  |         |         |         | ±0.05   |

Note 1: All dimensions exclude mold flash and end flash which shall not exceed 0.006" (0.15mm) per side. Note 2: Lead coplanarity 0.004" (0.1mm) max.

#### Marking

The product is marked with style, schematic code, TCR code, value and tolerance code.

All information is subject to TT Electronics' own data and is considered accurate at time of going to print.

# **SOIC Thin Film on Ceramic Resistor Networks**

**SOIC-C Series**

### **OBSOLETE**

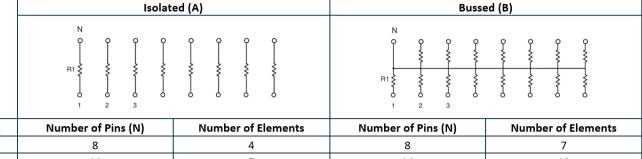

### **Schematic Data**

| Style    | Number of Pins (N) | Number of Pins (N) Number of Elements |    | Number of Elements |  |

|----------|--------------------|---------------------------------------|----|--------------------|--|

| GS4      | 8                  | 4                                     | 8  | 7                  |  |

| GS7      | 14                 | 14 7 14                               |    | 13                 |  |

| GS8, GL8 | 16                 | 8                                     | 16 | 15                 |  |

| GL0      | 20                 | 10                                    | 20 | 19                 |  |

### **Performance Data**

| Took you MIL DDF 92401    | ±ΔR/R%  |         |  |  |  |

|---------------------------|---------|---------|--|--|--|

| Test per MIL-PRF-83401    | Typical | Maximum |  |  |  |

| Thermal shock             | 0.02    | 0.1     |  |  |  |

| Power conditioning        | 0.03    | 0.1     |  |  |  |

| High temperature exposure | 0.03    | 0.05    |  |  |  |

| Short-time overload       | 0.02    | 0.05    |  |  |  |

| Low temperature storage   | 0.03    | 0.05    |  |  |  |

| Life                      | 0.05    | 0.1     |  |  |  |

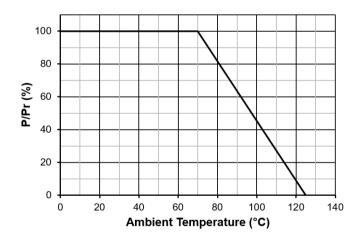

#### **Temperature Derating**

© TT Electronics plc

## **SOIC Thin Film on Ceramic Resistor Networks**

**SOIC-C Series**

### OBSOLETE

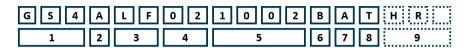

### **Ordering Procedure**

Example: GS4ALF021002BATHR (8-pin narrow SOIC, isolated elements, Pb-free, 50ppm/°C, 10 kilohms, absolute tolerance ±0.1%, ratio tolerance ±0.05%, tube packed, variant HR)

| 1     | 2            | 3            | 4               | 5          | 6                     | 7                  | 8        | 9                     |

|-------|--------------|--------------|-----------------|------------|-----------------------|--------------------|----------|-----------------------|

| Style | Schematic    | Termination  | Absolute TCR    | Value      | Absolute<br>Tolerance | Ratio<br>Tolerance | Packing  | Variant               |

| GS4   | A = Isolated | LF = Pb-free | 03 = ±25ppm/°C  | 3 digits + | B = ±0.1%             | A = ±0.05%         | T = Tube | Omit for standard     |

| GS7   | B = Bussed   | (100%Sn)     | 02 = ±50ppm/°C  | multiplier | C = ±0.25%            | $B = \pm 0.1\%$    | R = Reel | HR = High reliability |

| GS8   |              |              | 01 = ±100ppm/°C | R = ohms   | D = ±0.5%             | C = ±0.25%         |          | screened (50 cycles   |

| GL8   |              |              |                 | for values | F = ±1%               | D = ±0.5%          |          | thermal shock)        |

| GL0   |              |              |                 | <100 ohms  | G = ±2%               | F = ±1%            |          |                       |

|       |              |              | ·               |            | J = ±5%               | G = ±2%            |          |                       |

Note 1: Legacy part numbers may have the Variant code placed after the Schematic code, e.g. **GS4AHRLF021002BAT**.

Note 2: Legacy part numbers may be prefixed by GUL-, e.g. GUL-GS4ALF021002BATHR.

© TT Electronics plc

03.25