## Resistors

# Wire Bondable Chip Resistors

#### **WBC Series**

- Discrete or tapped schematics

- MIL inspection available

- High resistor density

All parts are Pb-free and comply with EU Directive 2011/65/EU amended by (EU) 2015/863 (RoHS3)

The WBC combines IRC's TaNSil® tantalum nitride thin film technology with silicon substrate processing to produce an extremely small tantalum nitride thin film technology with silicon substrate processing to produce an extremely small footprint device with the proven stability, reliability and moisture performance of IRC's TaNSil® resistor film.

Available in a wide range of tolerances and temperature coefficients to fit a variety of hybrid circuit applications. Custom resistance values, sizes and schematics are available on request from the factory.

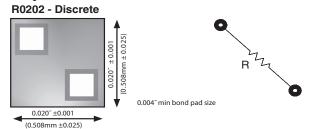

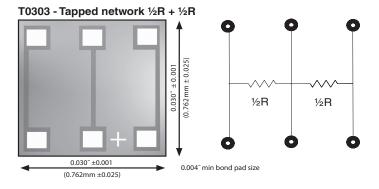

### Physical Data

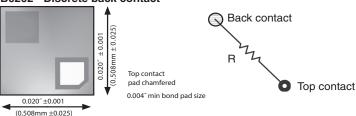

#### B0202 - Discrete back contact1

#### **Electrical Data**

| Absolute Tolerance                             |                    | to ±0.1%                                        |  |  |

|------------------------------------------------|--------------------|-------------------------------------------------|--|--|

| Absolute TCR                                   |                    | to ±25ppm/°C                                    |  |  |

| Package Power Rating<br>(@ 70°C)               |                    | 250mW                                           |  |  |

| Rated Operating Voltage (not to exceed √P x R) |                    | 100V                                            |  |  |

| Operating Temperature                          |                    | -55°C to +150°C                                 |  |  |

| Noise                                          |                    | <-30dB                                          |  |  |

| Substrate Material                             |                    | Oxidized Silicon<br>(10KÅ SiO <sub>2</sub> min) |  |  |

| Substrate Thickness                            |                    | 0.010" ±0.001<br>(0.254mm ±0.025)               |  |  |

| Bond Pad<br>Metallization                      | Aluminum           | 10KÅ minimum                                    |  |  |

|                                                | Gold <sup>1</sup>  | 15KÅ minimum                                    |  |  |

| Backside                                       | R0202 and<br>T0303 | Silicon<br>(Al / Au optional)                   |  |  |

|                                                | B0202 <sup>1</sup> | 3KÅ Au minimum<br>10KÅ Al minimum               |  |  |

| Passivation                                    |                    | Silicon Dioxide or<br>Silicon Nitride           |  |  |

Note 1: Not recommended for new designs

#### General Note

**WBC Series**

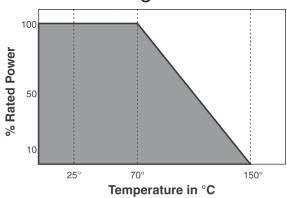

# **Power Derating Data**

# TCR/Inspection Code Table

| Absolute TCR | Commercial<br>Code | MIL Inspection<br>Code* |  |

|--------------|--------------------|-------------------------|--|

| ±300ppm/°C   | 00                 | 04                      |  |

| ±100ppm/°C   | 01                 | 05                      |  |

| ±50ppm/°C    | 02                 | 06                      |  |

| ±25ppm/°C    | 03                 | 07                      |  |

\*Notes: Product supplied to Class H of MIL-PRF 38534 includes 100% visual inspection

# Manufacturing Capabilities Data

| Resistance Range | Package       | Available Abs<br>Tolerances | Available Ratio Tol<br>(T0303 only) | Best Absolute<br>TCR | Tracking TCR<br>(T0303 only) |

|------------------|---------------|-----------------------------|-------------------------------------|----------------------|------------------------------|

| 10Ω - 20Ω        | 0202 only     | GJK                         | N/A                                 | +-100ppm/C           | N/A                          |

| 21Ω - 50Ω        | 0202 and 0303 | FGJK                        | FGJ                                 | +-100ppm/C           | +-50ppm/C                    |

| 51Ω - 100Ω       | 0202 and 0303 | CDFGJK                      | CDFGJ                               | +-100ppm/C           | +-25ppm/C                    |

| 101Ω - 200Ω      | 0202 and 0303 | CDFGJK                      | CDFGJ                               | +-50ppm/C            | +-10ppm/C                    |

| 201Ω - 500Ω      | 0202 and 0303 | BCDFGJK                     | BCDFGJ                              | +-50ppm/C            | +-5ppm/C                     |

| 501Ω - 999Ω      | 0202 and 0303 | BCDFGJK                     | BCDFGJ                              | +-25ppm/C            | +-2ppm/C                     |

| 1.0ΚΩ - 400ΚΩ    | 0202 and 0303 | BCDFGJK                     | A B C D F G J                       | +-25ppm/C            | +-2ppm/C                     |

| 401ΚΩ - 800ΚΩ    | 0303 only     | BCDFGJK                     | ABCDFGJ                             | +-25ppm/C            | +-2ppm/C                     |

## Wire Bondable **Chip Resistors**

## **Environmental Data**

| Test                         | Method                                          | Max R  | Typical R |

|------------------------------|-------------------------------------------------|--------|-----------|

| Thermal Shock                | MIL-STD-202<br>Method 107<br>Test condition F   | ±0.1%  | ±0.02%    |

| High Temperature Exposure    | MIL-STD-883<br>Method 1008<br>150°C, 1000 hours | ±0.1%  | ±0.05%    |

| LowTemperature Storage       | -55°C, 1000 hours                               | ±0.03% | ±0.01%    |

| Life                         | MIL-STD-202<br>Method 108<br>70°C, 1000 hours   | ±0.5%  | ±0.01%    |

| Life at Elevated Temperature | MIL-STD-202<br>Method 108<br>125°C, 1000 hours  | ±0.5%  | ±0.05%    |

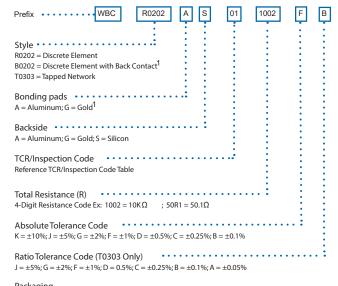

# **Ordering Data**

Standard packaging is 2" x 2" chip tray. For additional information or to discuss your specific requirements, please contact our Applications Team using the contact details below.

Note 1: Not recommended for new designs